This use case shows how to use GOF in timing ECO.

Load in library, lef, def and netlist by the following command

gof -lib tsmc_std.lib -lef tsmc_std.lef -def top.def top.v

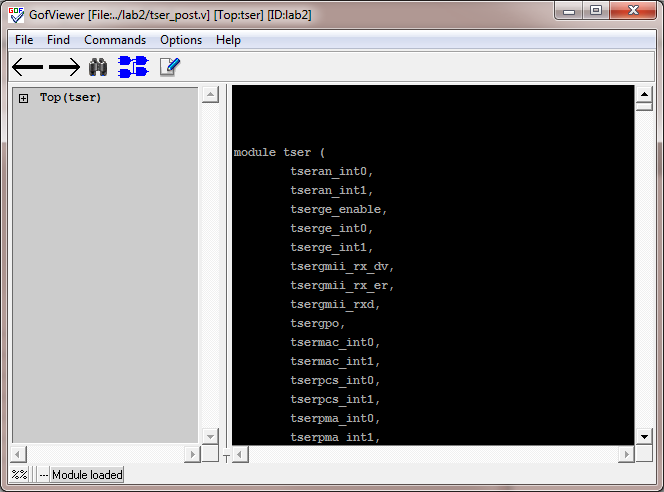

GofViewer window appears

Figure 1 GofViewer Window

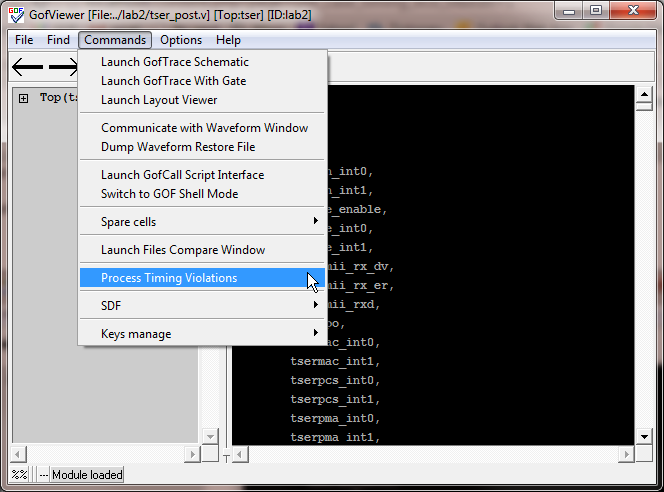

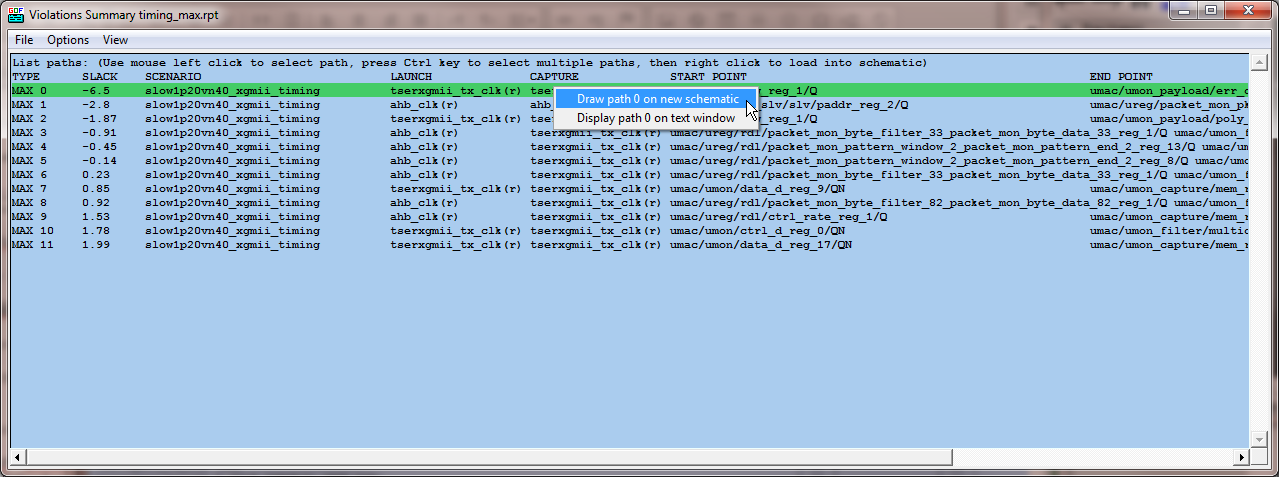

Figure 2 Process Timing Violations Command

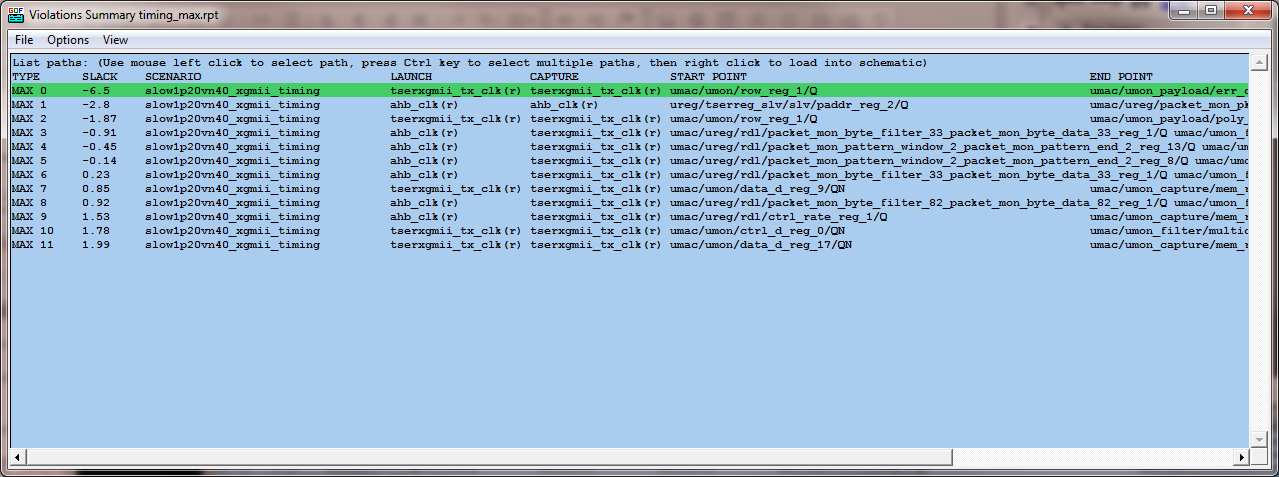

Figure 3 Violations Summary Window

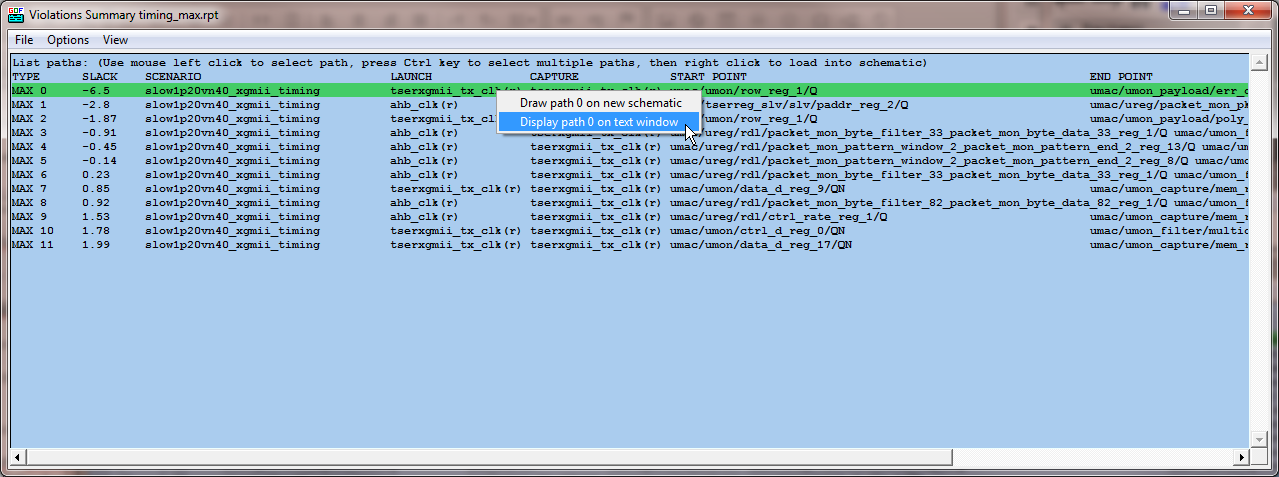

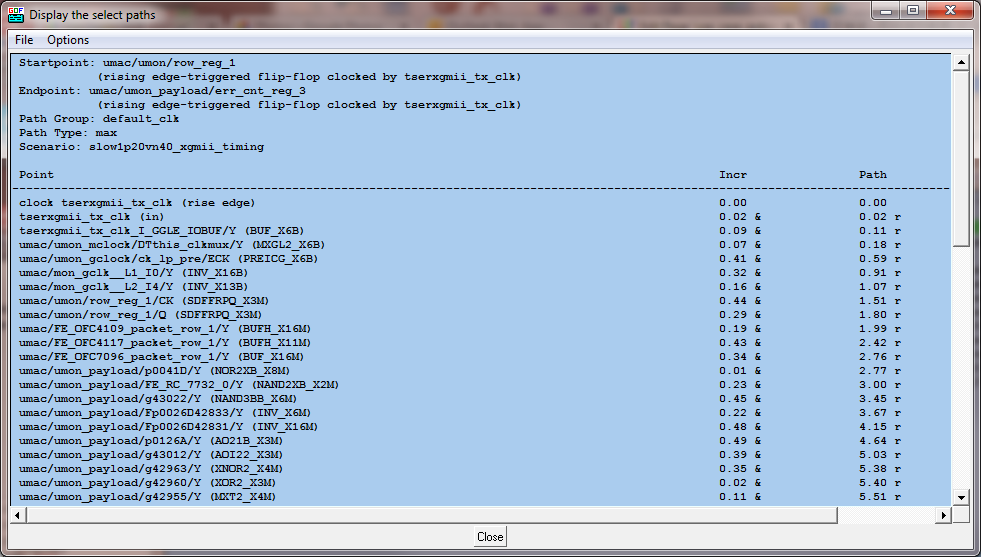

Figure 4 Choose display violation path in text mode

Figure 5 Display the path on text window

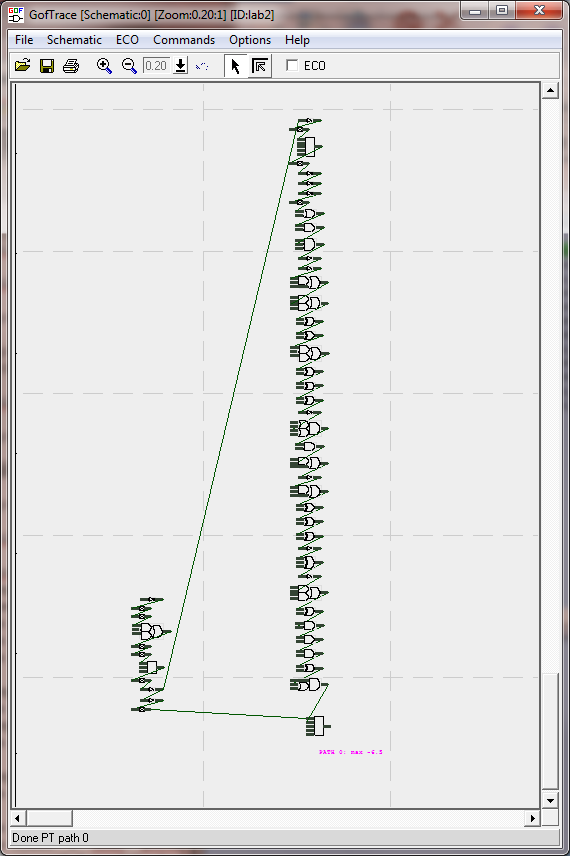

Figure 6 Choose draw schematic option

Figure 7 The whole path displayed on a schematic window

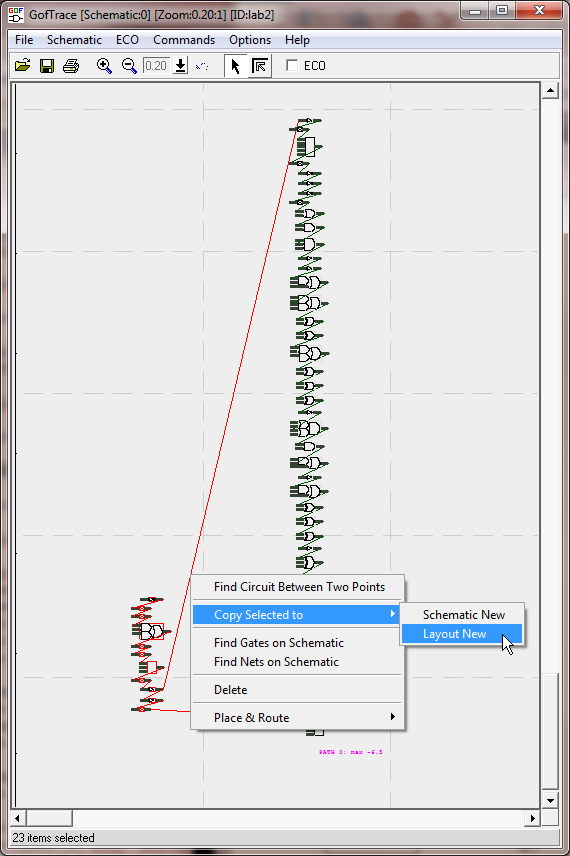

Figure 8 Select clock path and choose view on LayoutViewer window

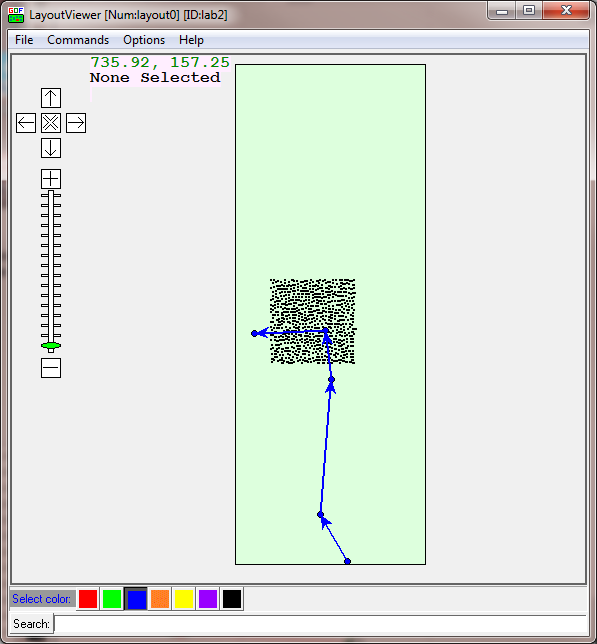

Figure 9 Clock path displayed on LayoutViewer window

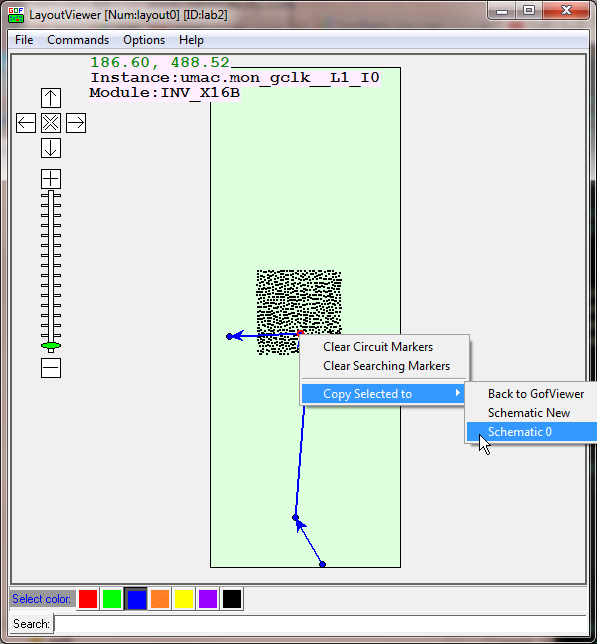

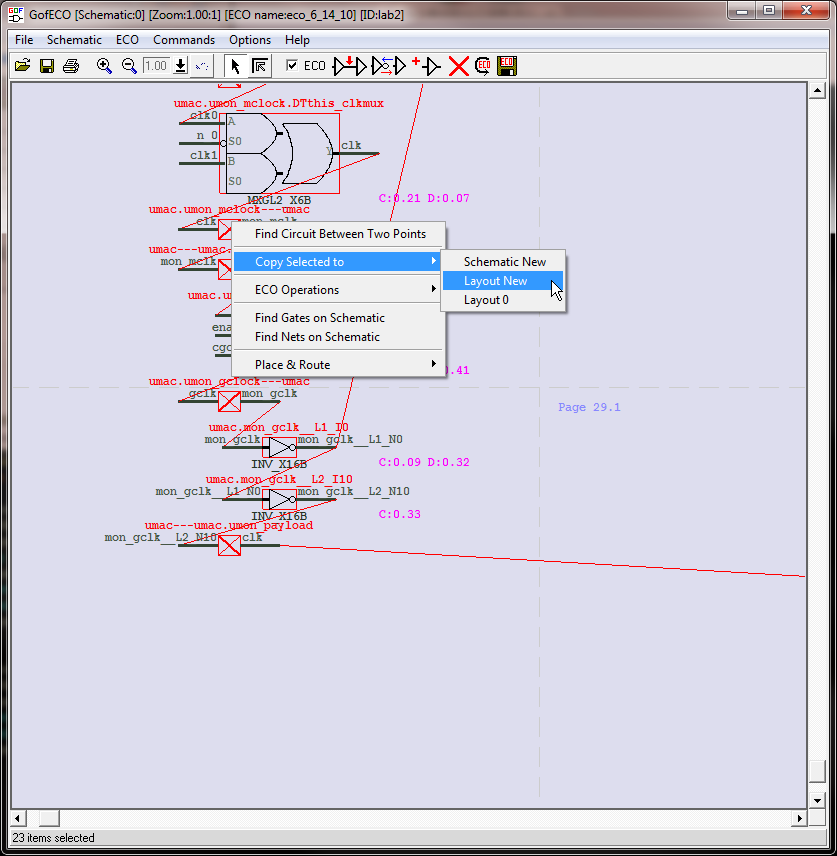

Figure 10 Send instances under ECO back to the schematic window

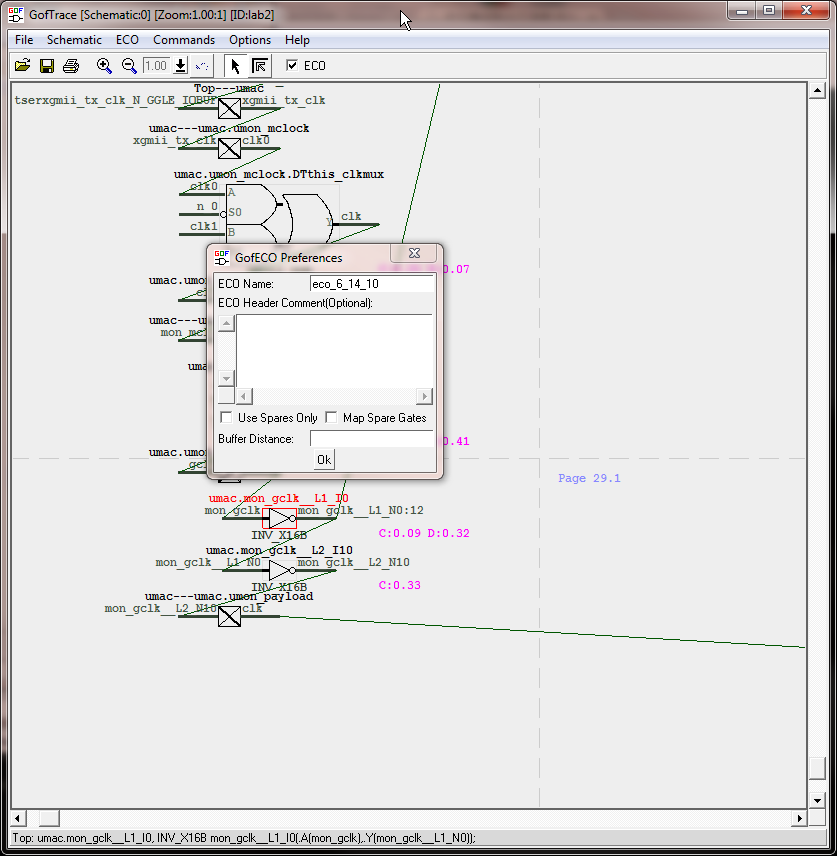

Figure 11 Enable ECO by check ECO button

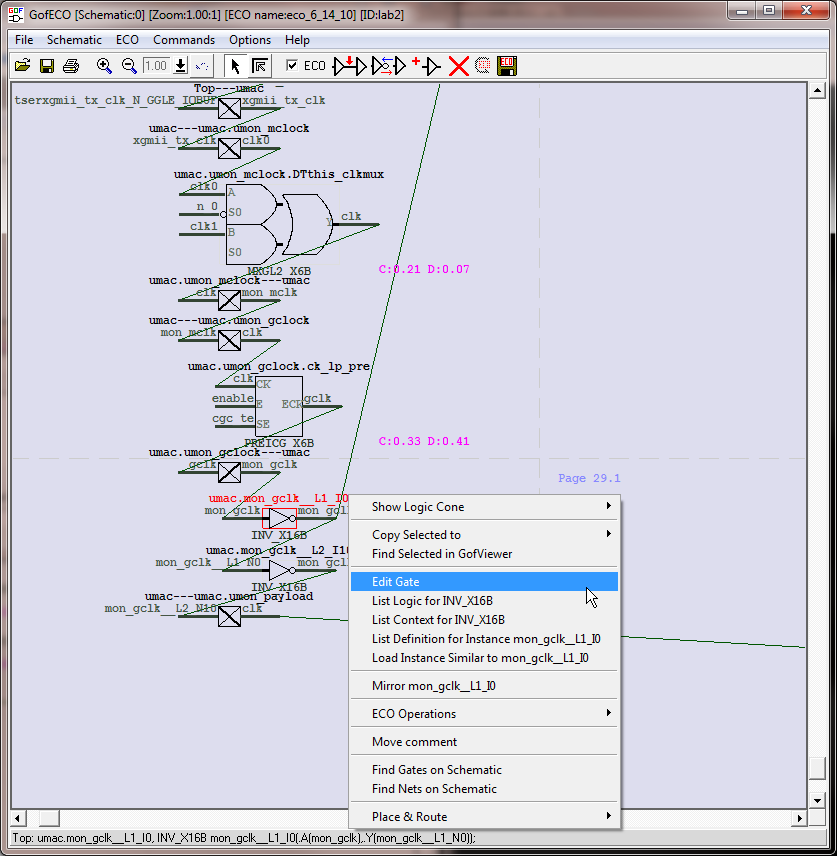

Figure 12 Choose 'Edit Gate' command

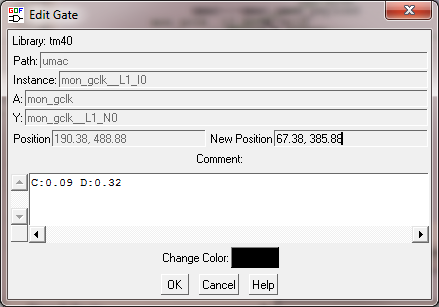

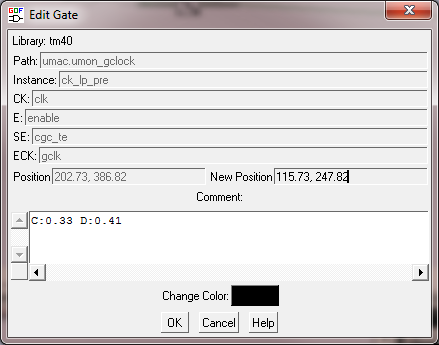

Figure 13 Fill in the New Position

Figure 14 Fill in the New Position for the other cells

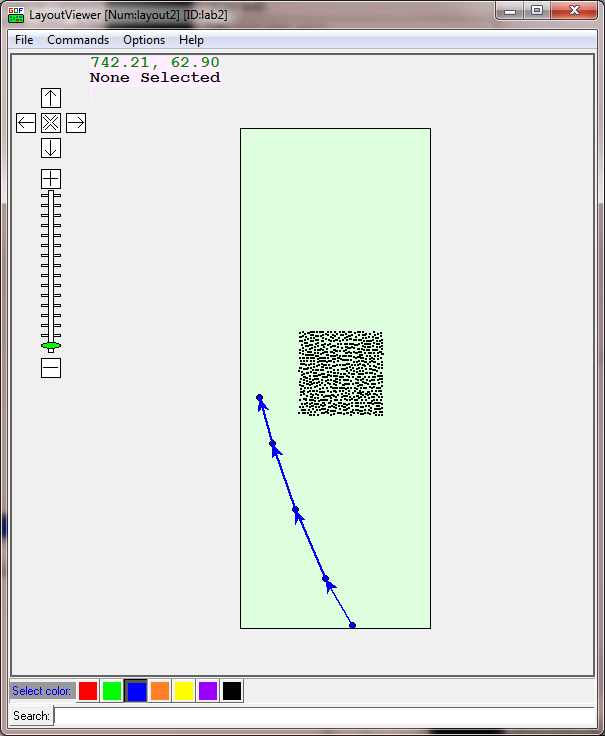

Figure 15 Select the clock path and send to a new LayoutViewer

Figure 16 To verify that the path after ECO is straight

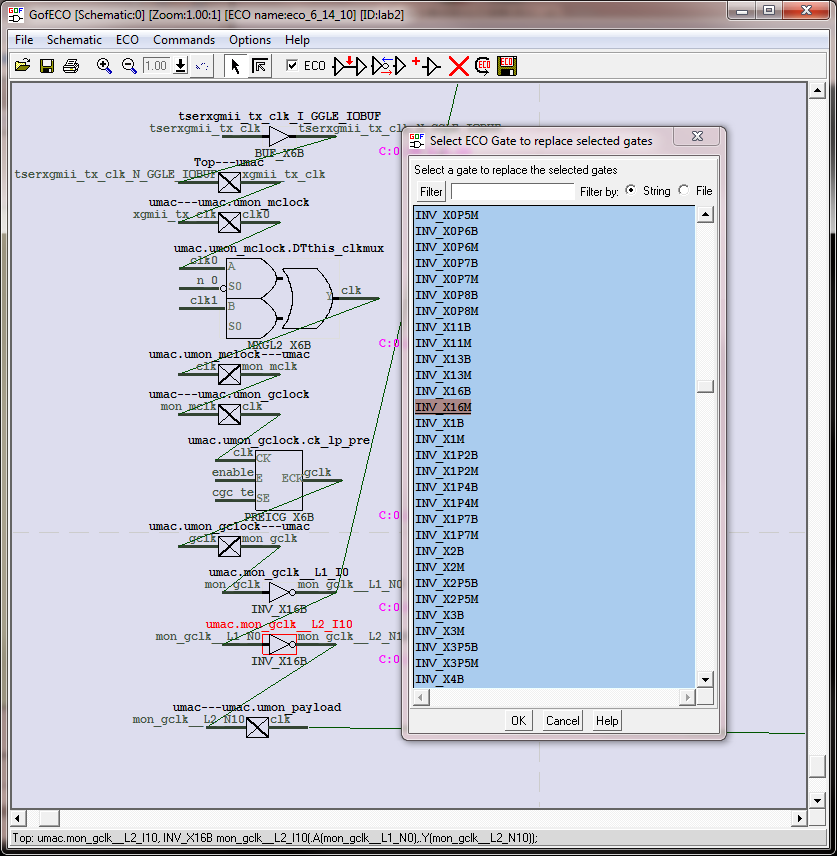

Figure 17 Upsize cells

The ECO result can be saved in in Verilog format, Synopsys TCL format and Cadence SOC Encounter ECO format.

Synopsys TCL format:

current_instance

current_instance umac/umon_gclock

set_cell_location -ignore_fixed -coordinates "115.73 247.82" ck_lp_pre

current_instance

current_instance umac

size_cell mon_gclk__L2_I10 INV_X16M

set_cell_location -ignore_fixed -coordinates "67.38 385.88" mon_gclk__L1_I0

Cadence SOC Encounter ECO format:

ecoChangeCell -inst umac/mon_gclk__L2_I10 -cell INV_X16M

MOVEINST umac/umon_gclock/ck_lp_pre [COORD 202.73 386.82 115.73 247.82]

MOVEINST umac/mon_gclk__L1_I0 [COORD 190.38 488.88 67.38 385.88]