The use case shows how to automatically fix a design in partial mode. When design is large, it's time consuming to run ECO from the most top level and it may bring redundant fixes. If all RTL changes are contained in one sub-module and its hierarchical instances, the top level module can be set to the sub-module, and run 'fix_design' on that sub-module.

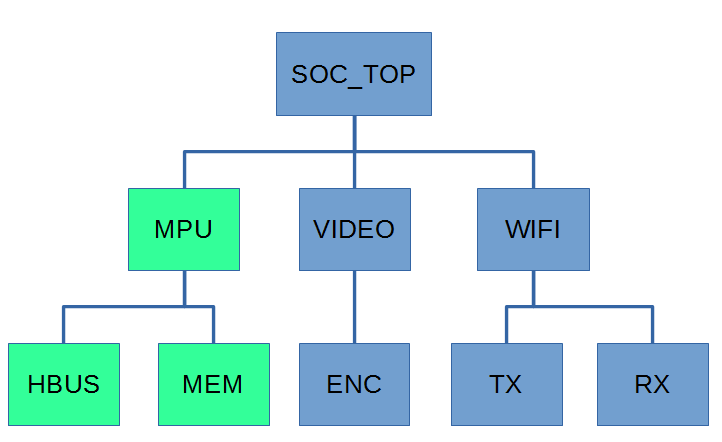

If design is large and ECO run time becomes too long, there is potentially a way to improve the speed. For a design shown in the following chart, if RTL changes are known to be contained inside module 'MPU' and its sub-modules, 'HBUS' and 'MEM', the top level can be set on 'MPU' and 'fix_design' can run much faster.

# GofCall ECO script, auto_eco.pl use strict; undo_eco; # Discard previous ECO operations setup_eco("eco_example"); # Setup ECO name read_library("art.90nm.lib"); # Read in standard library # Read in the Reference Netlist which is re-synthesized with several modules modified read_design("-ref", "reference.gv"); # Read in the implementation Netlist Which is under ECO read_design("-imp", "implementation.gv"); set_top("MPU"); # Set the top module on MPU instead of the most top SOC_TOP # Fix the top module MPU and its sub-modules, HBUS and MEM fix_design; report_eco(); # ECO report write_verilog("eco_verilog.v"); # Write out ECO result in Verilog write_soce("eco_soce.tcl"); # Write out TCL script for SOC Encounter exit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

The above script can be run by '-run' option in GOF command line:

The example is in the released package.

To run the example: