If a bug is found during chip testing, a metal only ECO may be required. However, if there is no spare gate integration in the design, there are still options available. Spare gates can be found within the design, including manually inserted ones, as well as the use of a redundant flip-flop and its logic cone. Additionally, after synthesis, it is common for some gates to have output floating, which can be utilized as spare gates.

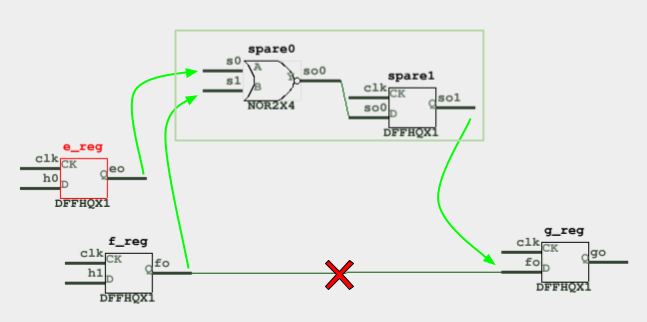

In this article, we will explore a use case where no spare gate integration is present in the design. The goal is to locate one NOR2 and one flip-flop elsewhere to complete the task. The objective of the ECO is to disconnect one connection and insert the NOR2 and flip-flop to drive the flop g_reg. Please note that the schematic has been simplified for the purposes of this discussion. It is important to note that all flip-flops should be scan type flops with a resettable pin and that they are all connected in the scan chain.

Figure 1: Metal only ECO to insert one NOR2 and Flop

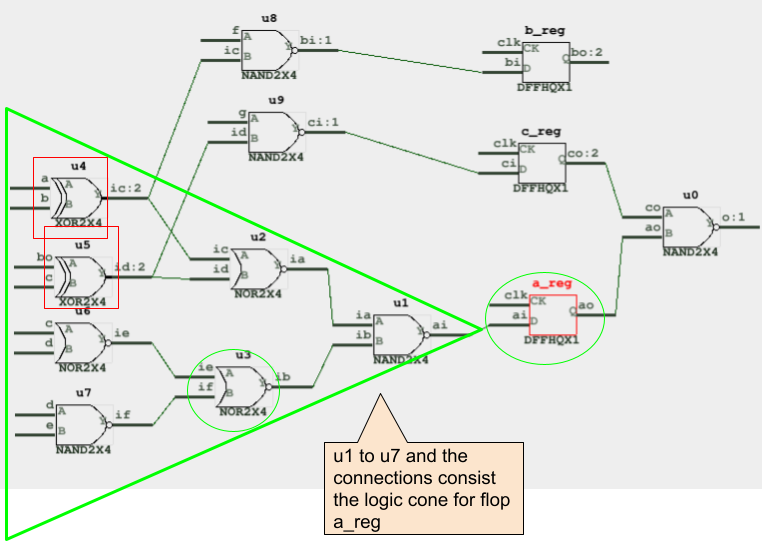

A logic cone refers to the combinational logic that drives a key point, such as a flop, an output, or an input port of a black box. In Figure 2, the flop a_reg is considered redundant by the designers, and its corresponding logic cone can be utilized in the metal only ECO. However, some instances within the logic cone are specifically dedicated to the a_reg flop, such as u1, u2, u3, u6, and u7. On the other hand, other instances are shared with another logic cones, such as u4 and u5. These shared instances cannot be removed and utilized in the ECO since they would affect the existing logic. For instance, u4 drives u8, which is part of the logic cone of flop b_reg. In this particular ECO, u3 can be used to replace NOR2 in Figure 1, and a_reg is used to replace the flop needed in the ECO.

Figure 2: Instances in a logic cone

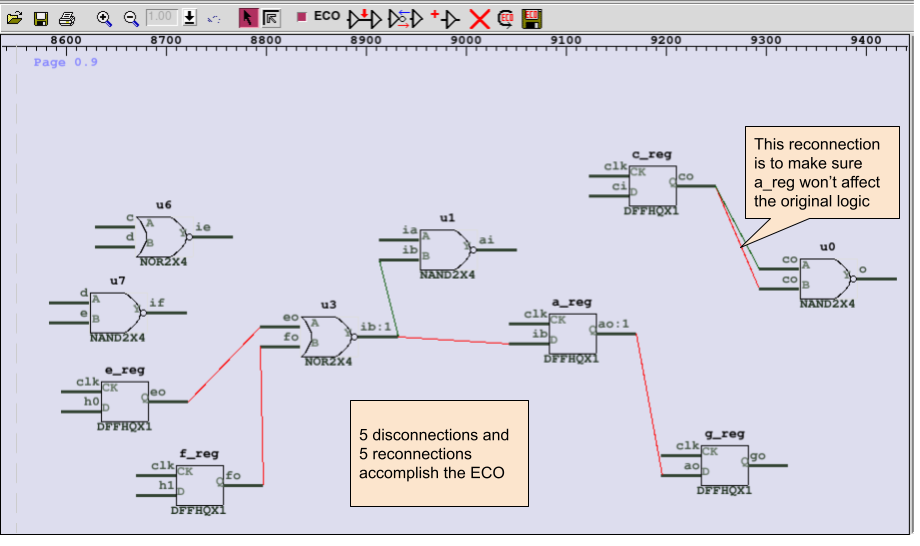

A text editor is typically used to modify a netlist, but this approach can be prone to errors and is not very efficient. More advanced methods for making modifications to netlists include automatic ECO, GUI schematic ECO, and script mode ECO. The current ECO method is well-suited for both schematic and script modes. GOF can perform ECO on the schematic in real-time, while GUI mode allows for ECO to be performed on the schematic with the use of mouse clicks. This ECO that involves one NOR2 and one flip-flop would require five disconnections and five re-connections.

Figure 3: GUI Schematic ECO

The ECO process can also be performed using script mode, which involves executing five change_pin operations that perform five wire cuts and connections.

setup_eco("eco_mo")

set_top("top");

change_pin("u3/A", "e_reg/Q");

change_pin("u3/B", "f_reg/Q");

change_pin("a_reg/D", "u3/Y");

change_pin("g_reg/D", "a_reg/Q");

change_pin("u0/B", "c_reg/Q");

One important consideration that has been overlooked in the above discussion of ECO is the impact on Design for Test (DFT). Specifically, the two flops, f_reg and g_reg, are actually back-to-back flops that serve both functional and scan chain purposes. When additional logic is inserted during the ECO process, the DFT functionality is broken.

To address this issue, the methods mentioned in the earlier may not be effective, as they are not designed to handle metal only ECOs, and the newly added gates may not be freely available. As a compromise solution, it may be necessary to remove g_reg from the original scan chain. While this may result in a minor loss of DFT coverage, it can help to ensure overall DFT performance.

The scan chain rework can be done by adding one more line in the ECO script:

setup_eco("eco_mo")

set_top("top");

change_pin("u3/A", "e_reg/Q");

change_pin("u3/B", "f_reg/Q");

change_pin("a_reg/D", "u3/Y");

change_pin("g_reg/D", "a_reg/Q");

change_pin("u0/B", "c_reg/Q");

change_pin("h_reg/SI", "f_reg/Q"); # Serve the purpose of bypassing g_reg

Functional Netlist ECO is a practical process. However, there is no single fixed mode or process that can be used to complete an ECO, as the specific approach taken depends on the stage of the design process in which the ECO is needed. In addition, an ECO may involve other design domains, such as Design for Test (DFT) and timing, which must also be taken into consideration. This underscores the importance of a flexible and adaptable approach to ECO, which can accommodate the unique needs and requirements of each design project.