Navigating Post-Layout ECO: Challenges and Solutions with GOF ECO

Post-layout Engineering Change Orders (ECOs) are modifications made to an integrated circuit design after the physical design (placement and routing) phase. Unlike pre-layout ECOs, which primarily focus on functional correctness and logical optimization, post-layout ECOs must also contend with stringent physical constraints, making them significantly more complex and challenging.

Key Challenges in Post-Layout ECO

The post-layout stage introduces several critical constraints that complicate ECO implementation:

- Physical Constraints: Changes must fit within the existing layout, respecting fixed cell placements, routing blockages, and limited available routing tracks. This often necessitates using only existing metal layers (metal-only ECO) to avoid costly and time-consuming mask re-spins.

- Timing Closure: Any modification can impact critical timing paths. Post-layout ECOs must ensure that timing violations are not introduced and, ideally, improve existing timing issues without creating new ones. This requires precise delay calculations and careful buffer/inverter insertion.

- Spare Cells: The availability and strategic placement of pre-inserted spare cells (unused gates) are crucial for metal-only ECOs. Without sufficient and appropriately located spare cells, implementing changes can become impossible or require full re-layout.

- Design Rule Checking (DRC) and Logic Equivalence Check (LEC): Post-ECO, the modified netlist must still pass all physical design rule checks and maintain logical equivalence with the original design (or the intended new functionality).

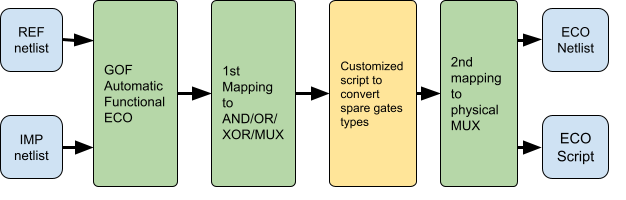

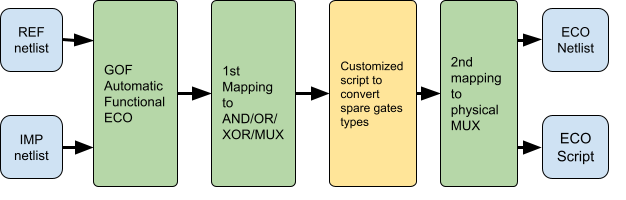

Figure 1: Post-Layout ECO: Physical Constraints and Spare Cell Utilization

As shown in Figure 1, post-layout ECO involves mapping functional patch to basic logic types and converting to the real optimal physical spare cells. The challenge lies in applying functional changes while respecting the fixed physical implementation.

GOF ECO's Solution for Post-Layout Challenges

GOF ECO provides a comprehensive solution designed to address the complexities of post-layout ECO, enabling efficient and reliable modifications:

- Physical Awareness: GOF ECO can read industry-standard LEF (Library Exchange Format) and DEF (Design Exchange Format) files. This allows the tool to understand the physical layout, including cell locations, routing blockages, and available space, ensuring that proposed changes are physically realizable.

- Automated Spare Cell Mapping: The tool intelligently identifies and utilizes pre-placed spare cells within the layout. It can automatically map new or modified logic onto these spare cells, minimizing the need for new cell placement and complex routing.

- Metal-Only ECO Capabilities: GOF ECO prioritizes metal-only changes, which are essential for avoiding mask re-spins. It optimizes logic to fit within existing routing layers and spare cell connections.

- Timing and Power Considerations: While primarily a functional ECO tool, GOF ECO's precise netlist manipulation helps in maintaining timing and power integrity. It allows for targeted buffer/inverter insertion and can be integrated into a larger timing-aware flow.

- Seamless Integration: GOF ECO integrates smoothly into existing design flows. Its output scripts can be directly used by physical design tools for final layout generation and verification.

- Robust LEC Verification: After any post-layout ECO, Logic Equivalence Checking (LEC) is paramount. GOF ECO's built-in LEC capabilities, or its ability to generate LEC-friendly output for third-party tools, ensures that the functional intent is preserved.

Example: Metal-Only ECO with Spare Cells

A common scenario in post-layout ECO is fixing a bug using available spare cells. The following script snippet demonstrates how GOF ECO can read physical information and map logic onto spare gates:

read_library("stdlib.lib");

read_design("-imp", "post_layout_netlist.v");

set_top("chip_top");

read_lef("tech.lef");

read_def("chip_top.def");

get_spare_cells("SPARE_CELL_INST_*"); # Identify spare cells based on naming convention

# ... (perform functional ECO changes, e.g., fix_design or manual changes) ...

map_spare_cells(); # Map the ECO logic onto available spare cells

report_spares(); # Report usage of spare cells

write_verilog("eco_post_layout.v");

This script illustrates the core steps: loading the physical layout data (LEF/DEF), identifying spare cells, performing the necessary logical modifications (which could be automatic or manual), and then mapping the new logic onto the identified spare cells. This process ensures that the ECO is physically implementable with minimal disruption to the layout.

Conclusion

Post-layout ECO is a critical and intricate phase in IC design. GOF ECO's specialized features, including physical awareness, automated spare cell mapping, and metal-only capabilities, empower designers to efficiently and reliably implement changes while adhering to strict physical and timing constraints. By streamlining this complex process, GOF ECO helps accelerate tape-out schedules and ensures the integrity of the final silicon.

Follow us:

© 2026 NanDigits Design Automation. All rights reserved.