Once a functional ECO has been performed, the resulting ECO patch can be synthesized to correspond with the available spare gates. These spare gates consist of a combination of two-input AND/OR/NAND/NOR/INV gates, as well as flops, with the optional inclusion of MUX gates.

The synthesis process can be constrained to ensure that only a certain number and type of spare gates are used. This is done using the API "set_constraint", which can be used to specify constraints on either the number or type of spare cells used.

It can be demonstrated that the optimal spare gates list consists solely of AND/OR/NAND/NOR gates. This can be shown by mapping AIO222X2 to various combinations of spare gates.

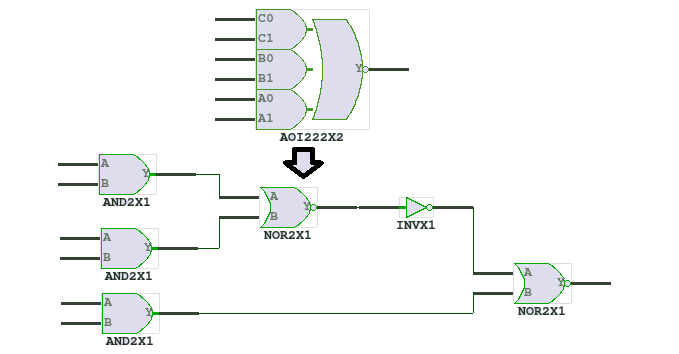

The following ECO script is to map AOI222X2 to AND2X1 and NOR2X1 types.

# LEC script, map_spare_cells_example.pl use strict; read_library("art.5nm.lib"); # Read in standard library read_design('-imp', 'imp_net.v'); change_port("out", "AOI222X2", "", "a,b,c,d,e,f"); set_constraints("-type", "AND2X1,INVX1,NOR2X1"); # Map to AND2X1/NOR2X1/INVX1 map_spare_cells; write_verilog("mapped_verilog.v");

As shown in Figure 1, 3 AND gates and 2 NOR are mapped in the final circuit.

Figure 1: Map Spare Cells to AND and NOR

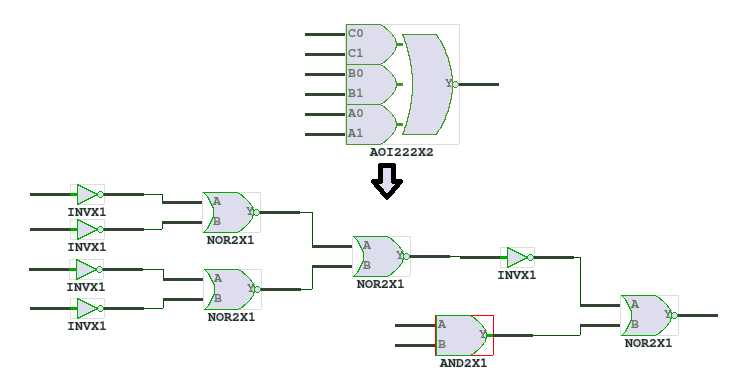

The following ECO script sets constraint to use only one AND.

# LEC script, map_spare_cells_example.pl use strict; read_library("art.5nm.lib"); # Read in standard library read_design('-imp', 'imp_net.v'); change_port("out", "AOI222X2", "", "a,b,c,d,e,f"); set_constraints("-type", "AND2X1,INVX1,NOR2X1"); set_constraints("-num", "and<2"); # Force to have only one 'and' type map_spare_cells; write_verilog("mapped_verilog.v");

As shown in Figure 2, 1 AND gates and 4 NOR are mapped in the final circuit. But 4 extra inverts are inserted.

Figure 2: Map Spare Cells to One AND and Multiple NOR

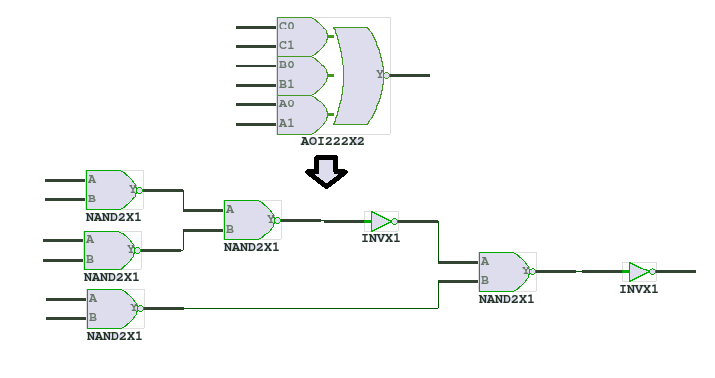

The following ECO script sets constraint to use only NAND type.

# LEC script, map_spare_cells_example.pl use strict; read_library("art.5nm.lib"); # Read in standard library read_design('-imp', 'imp_net.v'); change_port("out", "AOI222X2", "", "a,b,c,d,e,f"); set_constraints("-type", "INVX1,NAND2X1"); # Map to NAND2X1/INVX1 map_spare_cells; write_verilog("mapped_verilog.v");

Figure 3: Map Spare Cells to NAND

From the above experimental runs, the best constraint is to have spare cells type NAND, OR and NOR.

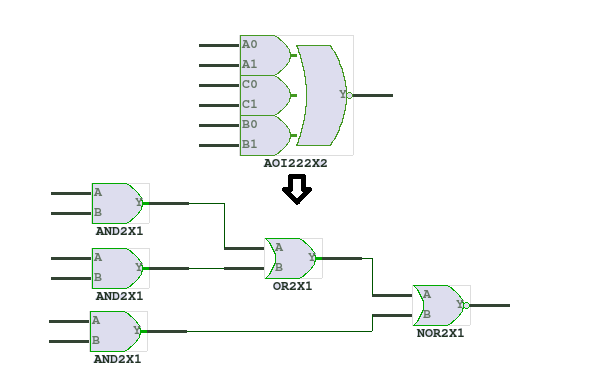

# LEC script, map_spare_cells_example.pl use strict; read_library("art.5nm.lib"); # Read in standard library read_design('-imp', 'imp_net.v'); change_port("out", "AOI222X2", "", "a,b,c,d,e,f"); set_constraints("-type", "AND2X1,INVX1,NOR2X1,OR2X1"); # Map to AND/OR/NOR map_spare_cells; write_verilog("mapped_verilog.v");

As shown in Figure 4, 3 AND, one OR and one NOR are used and no invert is used in this mapping.

Figure 4: Map Spare Cells to NAND

So the conclusion for the optimal spare gates list is, it should have AND/OR/NAND/NOR types spare gates. This will make synthesis work in most efficient way and ECO patch size is the smallest.

Check Metal Only ECO for detail