GOF AI is an agentic AI Platform that accelerates chip design. It revolutionizes interaction with EDA tools by enabling natural language commands for complex netlist ECO operations. It also generates Verilog RTL code directly from specifications, using a scoring system to help you select the most accurate version, and provides an automatic debugging method to quickly identify the root cause of non-equivalent points.

In the intricate world of Electronic Design Automation (EDA), engineers often face a steep learning curve when mastering complex tools. Remembering every API, its precise syntax, and the nuances of various options can be a significant hurdle, even for experienced users returning after a break. This frequently leads to repetitive consultations of user manuals, diverting valuable time from core design tasks.

The advent of cost-effective Large Language Models (LLMs) has opened a new paradigm: enabling users to interact with EDA tools using plain, natural language. This revolutionary approach allows engineers to simply describe their desired modifications, and the tool intelligently translates these instructions into executable commands.

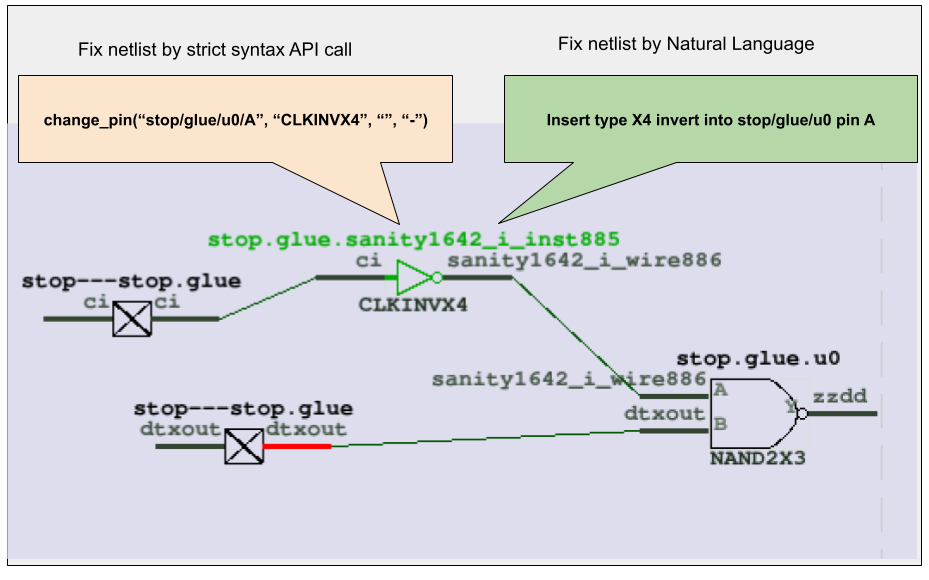

GOF ECO leverages this capability to introduce AI-Powered Natural Language ECO operations. As illustrated in Figure 1, users can now choose between the traditional, strict API syntax or a more intuitive natural language approach to perform complex netlist modifications, such as inserting a specific inverter type to alter a pin's logic.

Figure 1: Using Natural Language to Modify Netlist Logic

Traditionally, implementing a change like inserting an X4 inverter into a specific pin requires adherence to a precise API syntax. This often involves a detailed review of the user manual to locate the correct command and consulting the library file to identify the exact component name (e.g., 'CLKINVX4').

The Conventional API Call Method:

change_pin("stop/glue/u0/A", "CLKINVX4", "", "-")

With the LLM-driven approach, users can bypass manual searches and directly articulate their intent:

Insert type X4 invert into stop/glue/u0 pin A

At its core, the AI-powered Natural Language ECO in GOF operates through a sophisticated translation layer. When a user inputs a natural language command, the LLM processes it to:

Example script for Natural Language ECO operations:

# AI powered Natural Language ECO operations use strict; # To catch script syntax issue # Setup ECO name 'auto_svf' setup_eco("auto_svf_example"); read_library("/lib/5nm/tsmc_typ_85c_078v_svt.lib"); # Read in standard library read_design("-imp", "/proj/ai_acc/post/implementation.gv"); # Read in Implementation Netlist file Which is under ECO set_top("topmod"); set_ai(1); # Enable AI run_nl("Insert type X4 invert into stop/glue/u0 pin A"); # NL ECO run_nl("Change pin B of stop/glue/u0 to fun_clk"); run_nl("Insert a NAND into stop/glue/regsame/D pin, insert a MUX into B pin of the NAND, connect the MUX S0 pin to net bi, connect the Mux B pin to a new inserted AND gate, the AND gate is driven by net dft_clk and pin mmux0/du0/Y, connect the MUX A pin to net ci"); write_verilog("eco.gv");

In the rapidly evolving landscape of chip design, the ability to quickly and accurately translate high-level specifications into RTL code is paramount. Our advanced AI-powered solution revolutionizes this process by offering both full specification-to-RTL conversion and intelligent incremental RTL modification, ensuring high accuracy and efficiency.

Our platform enables designers to generate complete Verilog or SystemVerilog RTL code directly from comprehensive functional specifications. By leveraging sophisticated Large Language Models (LLMs) and deep learning techniques, the system interprets detailed design requirements, architectural descriptions, and behavioral logic provided in natural language or structured formats. This capability significantly accelerates the initial design phase, allowing engineers to rapidly prototype and explore design concepts without manual coding.

Beyond generating new designs, a critical challenge in chip development is efficiently modifying existing RTL. Our solution addresses this by supporting incremental RTL modifications based on partial specifications. Designers can provide targeted updates or bug fixes in natural language (e.g., 'add a new input port X and connect it to Y', 'change the behavior of module Z under condition W'). The AI agent intelligently analyzes the existing RTL, identifies the relevant sections, and generates only the necessary code changes. This approach minimizes disruption to the established design, preserves existing verification efforts, and drastically reduces the time and effort required for design iterations.

Achieving high accuracy in AI-generated RTL is crucial. To this end, our system employs a robust, multi-faceted scoring mechanism. When converting specifications to RTL, especially for complex logic, the AI generates multiple candidate RTL versions. Each version is then rigorously evaluated against a set of predefined criteria, which may include:

Example script for converting Spec to RTL:

read_library("-v", "the_lib_cells.v"); # optional set_ai_config('-fm_num', 1, '-algo_type', 4); set_ai_remote_server("localhost", 1998, 0, "___ENDQQ___", "___ENDAA___", "LLM_1_2_0"); spec_to_rtl("selection_to_resource.md");

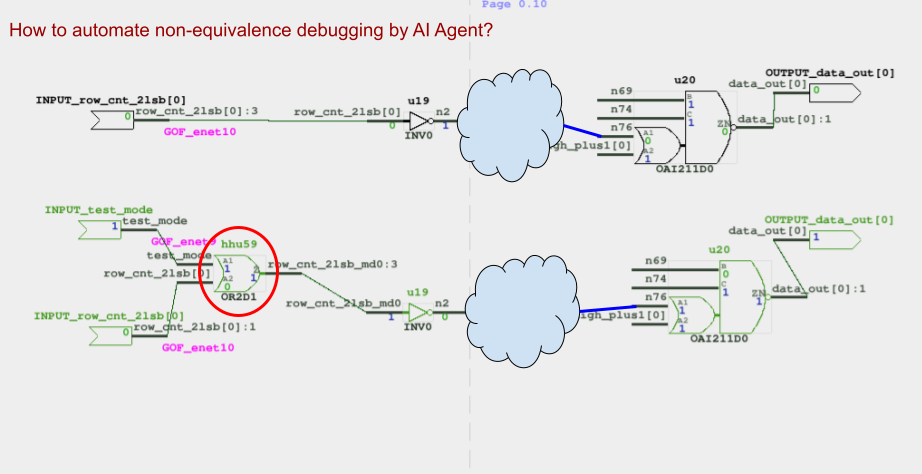

Chip designers have long faced a tedious, manual process when debugging non-equivalent points in a netlist—the discrepancies between a reference design and an implemented one. Even with tools like GOF Debug, which offer powerful features like counter-example tracing on schematics, the designer must still be an active participant. They're required to manually read logic values and click through the design to trace the issue back to its source.

Enter the new era of AI Agent-driven debug automation. By leveraging the power of Large Language Models (LLMs), the GOF platform is now capable of turning this manual, graphical process into a fully automated one, significantly reducing debugging time and effort.

Figure 2: How to automate the schematic non-equivalence debugging?

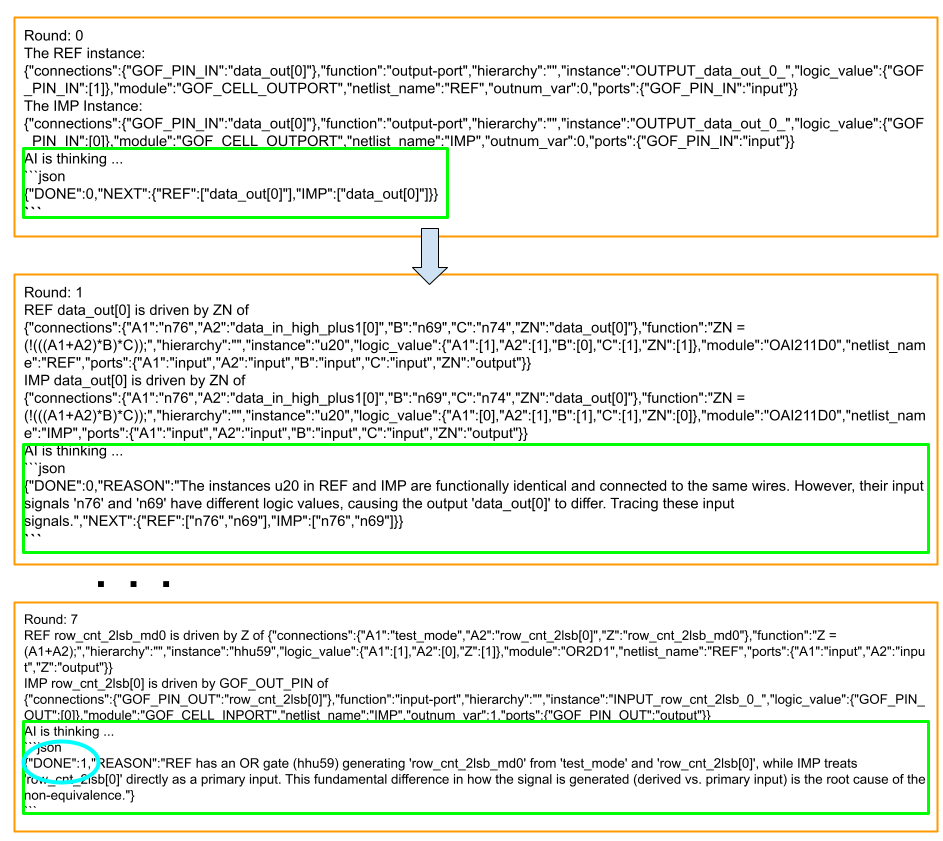

An AI agent, powered by a Large Language Model (LLM), automates the debugging process. Instead of a human, the AI agent takes charge.

Figure 3: AI Agent automates the debugging

Example script for AI Agent Non-equivalence debugging:

read_library("tsmc.lib"); read_design('-ref', "ref_netlist.v"); read_design('-imp', "imp_netlist.v"); set_ai_remote_server("localhost", 1998, 0, "___ENDQQ___", "___ENDAA___", "LLM_1_0_0"); ai_debug_noneq("data_out[0]");

This powerful AI agent-driven approach is not limited to just netlist non-equivalence issues. The same methodology can be applied to gate-level netlist simulation debugging. By feeding the AI agent with simulation waveforms and netlist data, it can analyze discrepancies between expected and simulated values. The agent then intelligently navigates the design to pinpoint the exact source of a functional error. This adaptability highlights the immense potential of AI agents to revolutionize a wide range of debugging and verification tasks throughout the entire chip design workflow.