In DFT flows, lockup latches or flops are typically inserted in two key locations:

This article discusses a hypothetical scenario where a metal-only ECO is required to insert lockup flops at scan output ports. The same approach can also be applied to other cases, such as inserting isolation cells. In this scenario, the design initially lacked lockup flops at the scan outputs, necessitating correction through an ECO process.

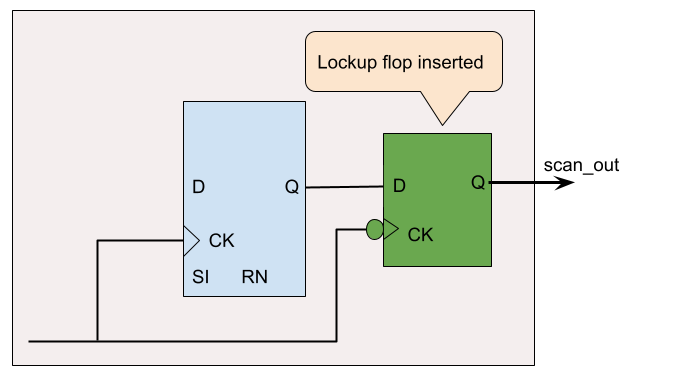

Figure 1: Lockup flop insertion to scan output

Lockup flops are inserted using a GOF ECO script. The process involves identifying scan output ports, inserting negedge-triggered flops, and mapping these to gate array spare cells.

This flexibility simplifies and enhances the efficiency of metal-only ECO implementation, particularly for complex, timing-critical scan paths or specialized flop requirements.

GOF utilizes ECO APIs to locate scan output ports and insert negedge-triggered flops.

# GOF script, dft_insert_lockup.pl use strict; read_library("tsmc.lib");# Read in standard library read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("SOC_TOP"); # Set the top to the most top module SOC_TOP my @so_ports = get_ports("scan_out*"); my $so_num = scalar(@so_ports); foreach my $so (@so_ports){ my @drv = get_driver($so, "-nonbuf"); my $drv_flop = $drv[0]; my $drv_pin = $drv[1]; my $lockup_inst = $so; $lockup_inst =~ s/\W/_/g; $lockup_inst .= "_lockup"; gprint("Inserting negedge flop as lockup to SO $so driven by $drv_flop/$drv_pin\n"); change_pin("$drv_flop/$drv_pin", "GDFFNQ_X1M_A9TH50", $lockup_inst, "$drv_flop/CK,-"); } read_lef("cell_lib.lef"); read_def("soc_top.def"); save_session("dft_insert_lockup"); get_spare_cells("-gate_array", "G*", "-gate_array_filler", "GFILL*"); map_spare_cells(); report_eco(); write_verilog("eco_verilog.v");# Write out ECO result in Verilog exit;

# ECO log file

...

FILLER_impl1_594 (GFILL4_A9TH50) @(156.18, 12.6) 4 Tiles used by the following instances. Fully used, deleted

u_gmii_tio/scan_out_12__lockup (GDFFNQ_X1M_A9TH50) TILE X 4

FILLER_impl1_14075 (GFILL4_A9TH50) @(70.49, 185.22) 4 Tiles used by the following instances. Fully used, deleted

u_mactop/u_prov_rst/scan_out_16__lockup (GDFFNQ_X1M_A9TH50) TILE X 4

FILLER_impl1_47975 (GFILL4_A9TH50) @(129.39, 579.6) 4 Tiles used by the following instances. Fully used, deleted

u_mactop/u_creg/u_rdl/scan_out_22__lockup (GDFFNQ_X1M_A9TH50) TILE X 4

FILLER_impl0_376 (GFILL8_A9TH50) @(91.96, 16.38) 4 Tiles used by the following instances. Changed to GFILL4_A9TH50

u_gre/u_dpth/u_fifo/scan_out_13__lockup (GDFFNQ_X1M_A9TH50) TILE X 4

Added Gates Used Total Tile Numbers: 96

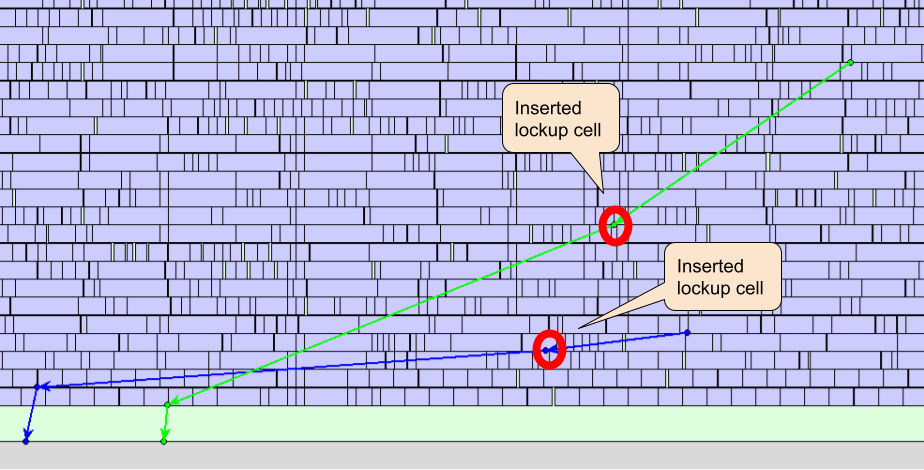

The actual placement confirms that both inserted lockup flops are positioned optimally within the design.

Figure 2: Lockup flops on the placement

This metal-only ECO approach effectively corrects missing lockup flops in scan outputs. By leveraging gate array spare cells, it simplifies the insertion process, ensuring robust DFT implementation without major design disruptions.