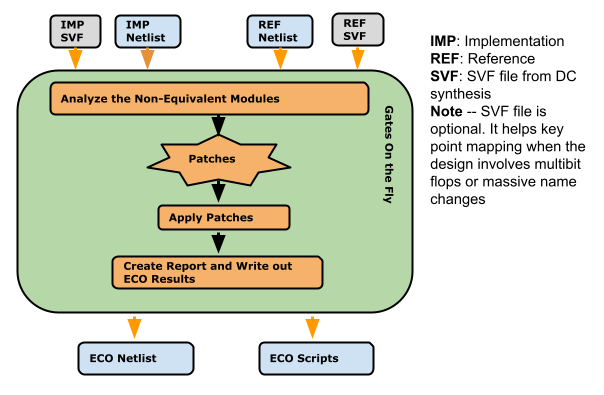

The Full Layers Functional ECO allows for the addition or removal of gates in a flexible manner. The ECO operations are performed using a script in Perl syntax, which accesses, modifies, and saves the netlist database using exported APIs. GOF ECO reads in two netlist files: the Implementation Netlist (which is under ECO) and the Reference Netlist (which is re-synthesized from modified RTL with the same constraints as the pre-layout netlist). In the ECO script, the 'fix_design' API is used to fix the top-level module and its sub-modules in global mode. GOF utilizes its built-in Logic Equivalent Check Engine to identify non-equivalent points and applies optimized minimum size gate patches to fix the non-equivalent modules.

Figure 1 shows that two logic cones are extracted from the Implementation and Reference Netlist for the same comparison point. Initially, the implementation point does not match the reference point. GOF compares the two points and generates a patch from the Reference logic cone, which it applies to the Implementation Netlist. After patching, the two points become equivalent.

Figure 1: Logic Cone Optimization

GOF performs logic cone analysis and optimization for each failing point discovered during top-down logic equivalence checks. The failing point takes the form of an output port or input pin of a sequential element, such as a flip-flop's D input. The final patch contains the fewest number of gates required to ensure that the implementation logic cone matches the reference logic cone.

Figure 2 depicts the flow chart of the process.

Figure 2: Automatic functional ECO flow

Steps for an automatic functional ECO:

The ECO script employs the exact syntax of a Perl script. It executes exported APIs that interact with the netlist database, facilitating modifications to the netlist.

The following is the example script for automatic functional ECO:

# GOF ECO script, run_example.pl use strict; setup_eco("eco_example");# Setup ECO name read_library("tsmc.5nm.lib");# Read in standard library # SVF files are optional, best to be used when the design involves multibit flops #read_svf("-ref", "reference.svf.txt"); # Optional, must be loaded before read_design, must be in text format #read_svf("-imp", "implementation.svf.txt"); # Optional, must be loaded before read_design, must be in text format read_design("-ref", "reference.gv");# Read in Reference Netlist read_design("-imp", "implementation.gv");# Read in Implementation Netlist Which is under ECO set_top("topmod");# Set the top module # Preserve DFT Test Logic set_ignore_output("scan_out*"); set_pin_constant("scan_enable", 0); set_pin_constant("scan_mode", 0); fix_design(); save_session("current_eco_name"); # Save a session for future restoration report_eco(); # ECO report check_design("-eco");# Check if the ECO causes any issue, like floating write_verilog("eco_verilog.v");# Write out ECO result in Verilog run_lec(); # Run GOF LEC to generate Formality help files gexit; # Exit when the ECO is done, comment it out to go to interactive mode when 'GOF >' appears

The ECO Script can be run by '-run' option.

Check Run and debug ECO script section in User Manual for more detail

Performing a complete top-level netlist synthesis can be time-consuming. GOF provides APIs enabling the integration of newly synthesized sub-modules into the original pre-layout netlist, along with updates to the top-level SVF file. This incremental approach allows the generation of the large top-level netlist and the top-level SVF file, resulting in significant time and effort savings. At the RTL level, designers identify modified RTL modules during ECO and synthesize them to create netlist and SVF files. Some altered RTL modules, particularly sub-parent modules with only sub-module instantiations, may not require synthesis.

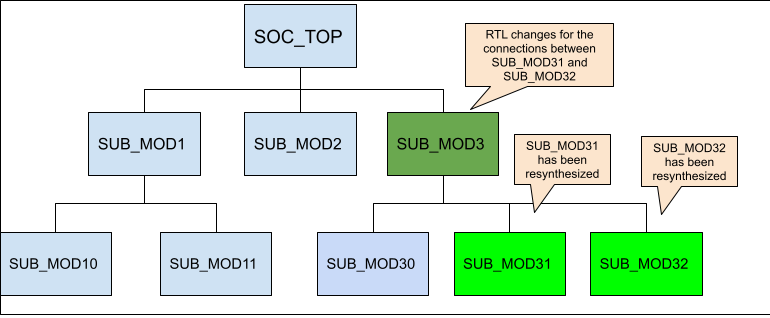

In Figure 3, only two sub-modules, SUB_MOD31 and SUB_MOD32, require re-synthesis in the extensive SOC_TOP design. Their parent module has only experienced connection changes and remains in netlist format, eliminating the need for synthesis. The example below illustrates how to process these files and generate a new SOC_TOP level netlist and SVF file.

Figure 3: Sub-modules to be synthesized

Step 1: Add missing DFT ports

The newly synthesized sub-modules may lack certain ports present in the original netlist. Notably, ports essential for scan in and scan out are typically added by the DFT tool. Since the DFT process is not applied to the new synthesized sub-modules, it's necessary to incorporate these ports as dummy ones within the modules to avoid syntax errors.

The procedure for incorporating DFT ports into the newly synthesized modules is as follows:

use strict; read_library("tsmc.lib"); read_design("-ref", "SOC_TOP.pre_layout.gv");# Read in the original pre_layout netlist read_design("-imp", "SUB_MOD31.new_syn.gv");# Read in new synthesized netlist set_tree("ref"); set_top("SUB_MOD31_1"); # The old pre-layout netlist may have this module with prefix or suffix added in uniquify my @ref_port_ins = get_ports("-input"); my @ref_port_outs = get_ports("-output"); set_tree("imp"); set_top("SUB_MOD31"); my @imp_port_ins = get_ports("-input"); my @imp_port_outs = get_ports("-output"); my $cnt = 0; foreach my $port (@ref_port_ins){ if(!grep($port eq $_, @imp_port_ins)){ # The input port is not in the new synthesized module new_port($port, "-input"); gprint("$cnt: Warning input $port is not in the new synthesized sub-module\n"); $cnt++; } } foreach my $port (@ref_port_outs){ if(!grep($port eq $_, @imp_port_outs)){ # The output port is not in the new synthesized module new_port($port, "-output"); gprint("$cnt: Warning output $port is not in the new synthesized sub-module\n"); $cnt++; } } write_verilog("SUB_MOD31.dft_ports_added.gv"); exit;

The identical process should be executed on SUB_MOD32 to include the necessary DFT-related ports.

Step 2: Replace sub-modules netlist and SVF

During this step, the DFT ports added netlist and SVF files of the synthesized sub-modules are read to substitute the original pre-layout netlist and SVF files.

The procedure for replacing netlist and SVF:

read_library("tsmc.lib"); read_svf("-imp", "SOC_TOP.pre_layout.svf"); read_design("-imp", "SOC_TOP.pre_layout.gv"); read_sub_module_svf("SUB_MOD31.svf.txt", "-module", "SUB_MOD31_1", "-syn_module", "SUB_MOD31"); read_sub_module_svf("SUB_MOD32.svf.txt", "-module", "SUB_MOD32_1", "-syn_module", "SUB_MOD32"); read_sub_module_netlist("SUB_MOD31.dft_ports_added.gv", "-module", "SUB_MOD31_1", "-syn_module", "SUB_MOD31"); read_sub_module_netlist("SUB_MOD32.dft_ports_added.gv", "-module", "SUB_MOD32_1", "-syn_module", "SUB_MOD32"); read_sub_module_netlist("SUB_MOD3.new.v", "-module", "SUB_MOD3_1", "-syn_module", "SUB_MOD3", "-sub_only"); # Need sub_only option replace_sub_module_netlist("SOC_TOP.new_reference.gv"); # Replace netlist should be run first replace_sub_module_svf("SOC_TOP.new_reference.svf"); # Then replace SVF

After the generation of both the top-level netlist and SVF files, they can be incorporated into the complete top-level automatic ECO process.

When working with designs that include multibit flops or significant name changes, SVF files can be a valuable tool for facilitating key point mapping. Although multibit flops are used to reduce silicon area and power consumption, the different combinations of single bit flop instances in each multibit flop instance can create challenges for key point mapping, especially when combined with name changes. Additionally, backend tools may split or merge multibit flops, further complicating the process. To avoid these challenges and ensure accurate key point mapping, it's highly recommended to load SVF files when working with multibit flops. For more information on this topic, please refer to the Multibit Flops in ECO section.

The example is in the released package.

To run the example:

The log file shows there are total 35 gates in the initial logic cone. After optimization, the patch has only 1 complex cell and 8 inverts