Introduction

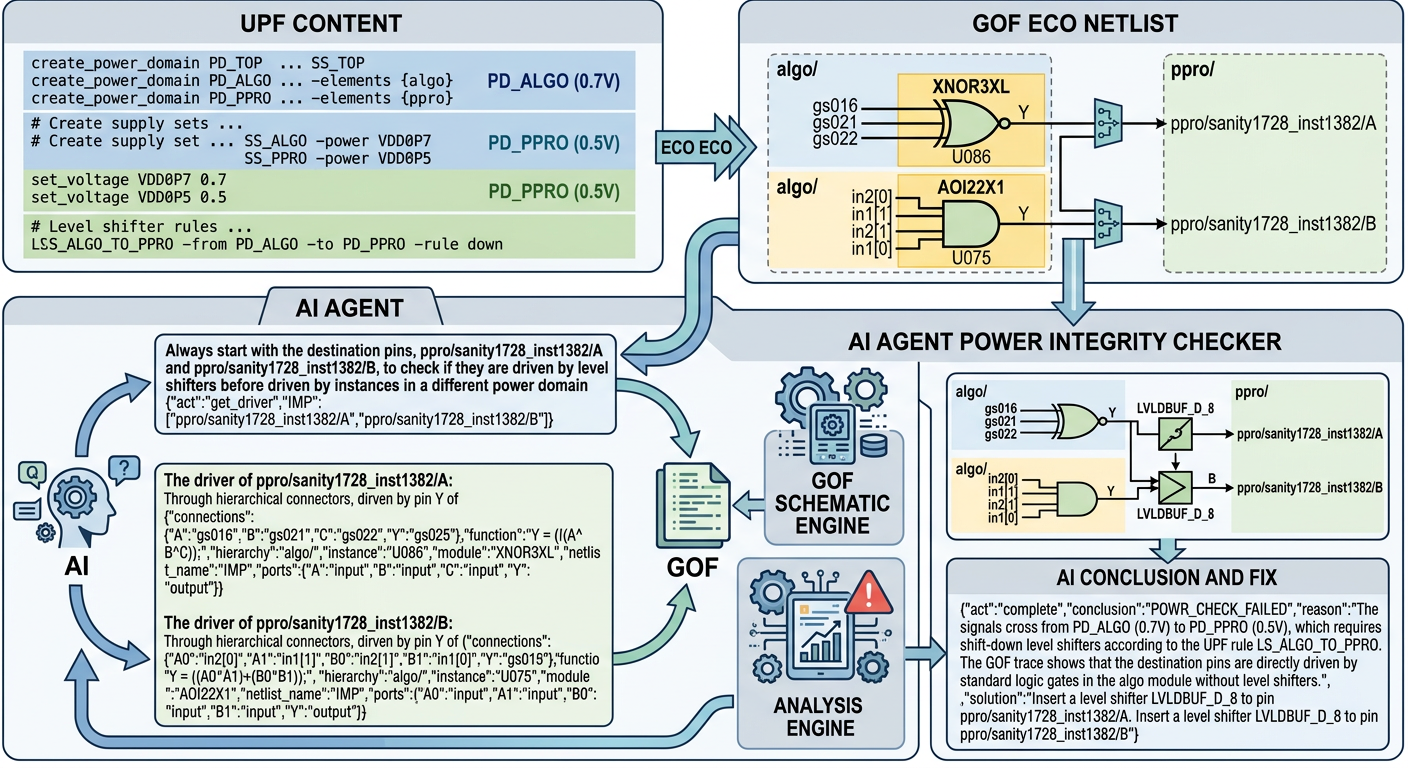

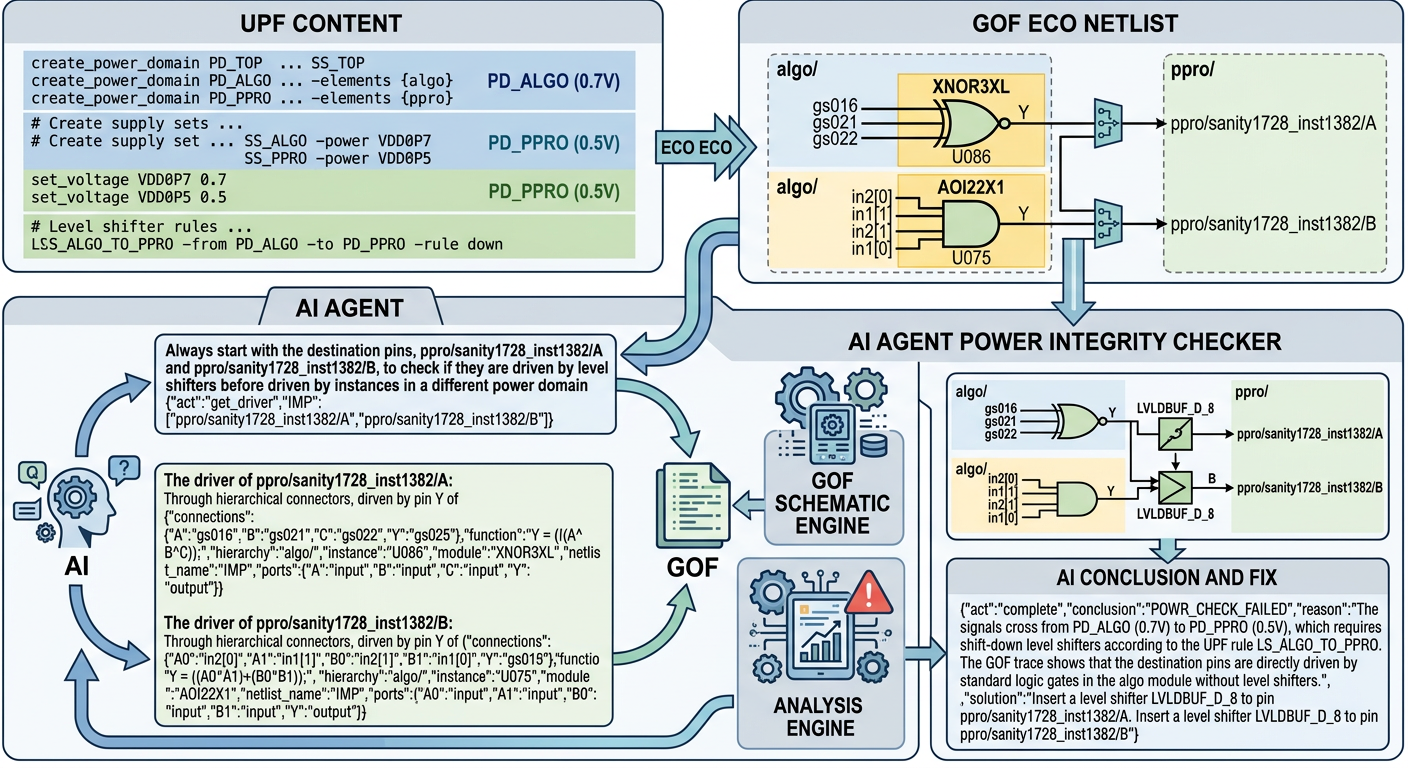

During a functional netlist ECO, the insertion of new logic gates often introduces signals that must traverse disparate power domains, making the preservation of power integrity a critical priority. If necessary level shifters are omitted during this stage, the resulting violations can remain undetected for a significant duration, leading to expensive delays. This risk is amplified by the highly specialized nature of modern IC design pipelines, where work assignments are strictly siloed. Functional ECO engineers typically focus on logic modifications while a separate power group handles compliance checking much further downstream. To eliminate this bottleneck, GOF ECO integrates with AI Agents to automatically validate the modified netlist against the Unified Power Format specification. This integration allows the tool to verify power flow compliance in real time after functional ECO, ensuring that all cross-domain signals are properly handled before the design moves to the next phase of the flow.

By facilitating a conversation between the AI Agent and the GOF schematic engine, the AI can trace signal drivers, evaluate power domains, conclude whether the ECO passes the power checker, and provide actionable solutions to comply with the UPF.

UPF Power Domain Configuration

The design defines multiple power domains with varying voltage levels. According to the UPF file, the relevant domains and level shifter rules are:

| Power Domain |

Voltage |

Scope/Elements |

| PD_ALGO |

0.7V |

algo |

| PD_PPRO |

0.5V |

ppro |

The UPF explicitly requires a shift-down level shifter when signals cross from PD_ALGO to PD_PPRO:

# From ALGO (0.7V) to PPRO (0.5V)

set_level_shifter LS_ALGO_TO_PPRO \

-from PD_ALGO \

-to PD_PPRO \

-rule down \

-location automatic

AI and GOF Interaction: Tracing the ECO

After GOF inserts the new gates, the AI Agent initiates a check on the destination pins to verify if they are properly driven by level shifters before crossing power domains.

[AI]: Always start with the destination pins, ppro/sanity1728_inst1382/A and ppro/sanity1728_inst1382/B, to check if they are driven by level shifters before driven by instances in a different power domain {"act":"get_driver","IMP":["ppro/sanity1728_inst1382/A","ppro/sanity1728_inst1382/B"]}

[GOF]: The driver of ppro/sanity1728_inst1382/A: Through hierarchical connectors, driven by pin Y of {"connections":{"A":"gs016","B":"gs021","C":"gs022","Y":"gs025"},"function":"Y = (!(A^B^C));","hierarchy":"algo/","instance":"U086","module":"XNOR3XL","netlist_name":"IMP","ports":{"A":"input","B":"input","C":"input","Y":"output"}}

The driver of ppro/sanity1728_inst1382/B: Through hierarchical connectors, dirven by pin Y of {"connections":{"A0":"in2[0]","A1":"in1[1]","B0":"in2[1]","B1":"in1[0]","Y":"gs015"},"function":"Y = (!((A0*A1)+(B0*B1)));","hierarchy":"algo/","instance":"U075","module":"AOI22X1","netlist_name":"IMP","ports":{"A0":"input","A1":"input","B0":"input","B1":"input","Y":"output"}}

Conclusion and Automated Fix

Based on the GOF trace, the AI Agent detects that the destination pins in the ppro module (0.5V) are directly driven by standard logic gates (XNOR3XL and AOI22X1) in the algo module (0.7V) without the required level shifters.

[AI]: {"act":"complete",

"conclusion":"POWR_CHECK_FAILED",

"reason":"The signals cross from PD_ALGO (0.7V) to PD_PPRO (0.5V), which requires shift-down level shifters according to the UPF rule LS_ALGO_TO_PPRO. The GOF trace shows that the destination pins are directly driven by standard logic gates in the algo module without level shifters.",

"solution":"Insert a level shifter LVLDBUF_D_8 to pin ppro/sanity1728_inst1382/A. Insert a level shifter LVLDBUF_D_8 to pin ppro/sanity1728_inst1382/B"}

Resolution: The AI successfully identifies the UPF violation and provides the exact ECO fix: inserting the LVLDBUF_D_8 level shifter cells on the violating pins to ensure power compliance.